Одними из очень важных элементов цифровой техники, а особенно в компьютерах и системах управления являются шифраторы и дешифраторы.

Когда мы слышим слово шифратор или дешифратор, то в голову приходят фразы из шпионских фильмов. Что-то вроде: расшифруйте депешу и зашифруйте ответ.

В этом нет ничего неправильного, так как в шифровальных машинах наших и зарубежных резидентур используются шифраторы и дешифраторы.

Шифраторы.

Таким образом, шифратор (кодер), это электронное устройство, в данном случае микросхема, которая преобразует код одной системы счисления в код другой системы. Наибольшее распространение в электронике получили шифраторы, преобразующие позиционный десятичный код, в параллельный двоичный. Вот так шифратор может обозначаться на принципиальной схеме.

К примеру, представим, что мы держим в руках обыкновенный калькулятор, которым сейчас пользуется любой школьник.

Поскольку все действия в калькуляторе выполняются с двоичными числами (вспомним основы цифровой электроники), то после клавиатуры стоит шифратор, который преобразует вводимые числа в двоичную форму.

Все кнопки калькулятора соединяются с общим проводом и, нажав, к примеру, кнопку 5 на входе шифратора, мы тут же получим двоичную форму данного числа на его выходе.

Конечно же, шифратор калькулятора имеет большее число входов, так как помимо цифр в него нужно ввести ещё какие-то символы арифметических действий, поэтому с выходов шифратора снимаются не только числа в двоичной форме, но и команды.

Если рассмотреть внутреннюю структуру шифратора, то несложно убедиться, что он выполнен на простейших базовых логических элементах .

Во всех устройствах управления, которые работают на двоичной логике, но для удобства оператора имеют десятичную клавиатуру, используются шифраторы.

Дешифраторы.

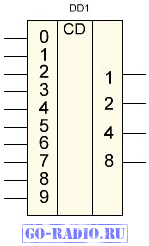

Дешифраторы относятся к той же группе, только работают с точностью до наоборот. Они преобразуют параллельный двоичный код в позиционный десятичный. Условное графическое обозначение на схеме может быть таким.

Или таким.

Если говорить о дешифраторах более полно, то стоит сказать, что они могут преобразовывать двоичный код в разные системы счисления (десятичную, шестнадцатиричную и пр.). Всё зависит от конкретной цели и назначения микросхемы.

Простейший пример . Вы не раз видели цифровой семисегментный индикатор, например, светодиодный. На нём отображаются десятичные цифры и числа к которым мы привыкли с детства (1, 2, 3, 4...). Но, как известно, цифровая электроника работает с двоичными числами, которые представляют комбинацию 0 и 1. Что же преобразовало двоичный код в десятичный и подало результат на цифровой семисегментный индикатор? Наверное, вы уже догадались, что это сделал дешифратор.

Работу дешифратора можно оценить вживую, если собрать несложную схему, которая состоит из микросхемы-дешифратора К176ИД2 и светодиодного семисегментного индикатора, который ещё называют «восьмёркой». Взгляните на схему, по ней легче разобраться, как работает дешифратор. Для быстрой сборки схемы можно использовать беспаечную макетную плату .

Для справки. Микросхема К176ИД2 разрабатывалась для управления 7-ми сегментным светодиодным индикатором. Эта микросхема способна преобразовать двоичный код от 0000 до 1001 , что соответствует десятичным цифрам от 0 до 9 (одна декада). Остальные, более старшие комбинации просто не отображаются. Выводы C, S, K являются вспомогательными.

У микросхемы К176ИД2 есть четыре входа (1, 2, 4, 8). Их ещё иногда обозначают D0 - D3 . На эти входы подаётся параллельный двоичный код (например, 0001). В данном случае, двоичный код имеет 4 разряда. Микросхема преобразует код так, что на выходах (a - g ) появляются сигналы, которые и формируют на семисегментном индикаторе десятичные цифры и числа, к которым мы привыкли. Так как дешифратор К176ИД2 способен отобразить десятичные цифры в интервале от 0 до 9, то на индикаторе мы увидим только их.

Ко входам дешифратора К176ИД2 подключены 4 тумблера (S1 - S4), с помощью которых на дешифратор можно подать параллельный двоичный код. Например, при замыкании тумблера S1 на 5 вывод микросхемы подаётся логическая единица. Если же разомкнуть контакты тумблера S1 - это будет соответствовать логическому нулю. С помощью тумблеров мы сможем вручную устанавливать на входах микросхемы логическую 1 или 0. Думаю, с этим всё понятно.

На схеме показано, как на входы дешифратора DD1 подан код 0101. На светодиодном индикаторе отобразится цифра 5. Если замкнуть только тумблер S4, то на индикаторе отобразится цифра 8. Чтобы записать число от 0 до 9 в двоичном коде достаточно четырёх разрядов: a 3 * 8 + a 2 * 4 + a 1 * 2 + a 0 * 1 , где a 0 - a 3 , - это цифры из системы счисления (0 или 1).

Представим число 0101 в десятичном виде 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5 . Теперь взглянем на схему и увидим, что вес разряда соответствует цифре, на которую умножается 0 или 1 в формуле.

Дешифратор на базе технологии ТТЛ - К155ИД1 использовался в своё время для управления газоразрядным цифровым индикатором типа ИН8, ИН12, которые были очень востребованы в 70-е годы, так как светодиодные низковольтные индикаторы ещё были очень большой редкостью.

Всё изменилось в 80-е годы. Можно было свободно приобрести семисегментные светодиодные матрицы (индикаторы) и среди радиолюбителей прокатился бум сборки электронных часов. Самодельные электронные часы не собрал для дома только ленивый.

.

Микросхема К176ИД1, К561ИД1

Неполный двоично-десятичный дешифратор имеет 4 входа для приема двоичного кода и 10 выходов его десятичного эквивалента.

Активный уровень и входа и выхода – высокий. При подаче на микросхему двоичного кода в диапазоне 8-15 на всех выходах устанавливается низкий логический уровень (дешифрация не производится). Дополнительных входов для стробирования микросхема не имеет, тем не менее, расширение разрядности несложно реализовать, если пожертвовать двумя последними десятичными разрядами:

В приведенной схеме в качестве стробирующего сигнала для DD2 используется инвертированный старший разряд входного кода. При этом выводы 4,5 (старшие десятичные разряды 8,9) микросхем не используются, а схема представляет собой полный двоично-десятичный дешифратор на 4 бита.

На следующем рисунке за счет использования отдельной микросхемы для управления дешифраторами число выходов увеличено до 64 (6-ти байтный входной код).

——————————————-

Микросхема К176ИД2

Дешифратор-преобразователь. Предназначен для преобразования двоичного кода в код для семисегментного индикатора. Цепей для управления десятичной точкой в микросхеме не предусмотрено. Кроме собственно дешифратора микросхема имеет триггер-защелку, позволяющий запоминать текущие данные.

Имеет четырехразрядный вход данных и семь выходов для подключения семисегментного цифрового индикатора. Активные уровни входа и выхода высокие, но при необходимости могут инвертироваться сигналом по служебному входу S. При низком уровне на этом входе активный выходной сигнал высокий, при «1» на S – низкий. Это позволяет подключать цифровые матрицы как с общим анодом, так и с общим катодом без дополнительных инверторов. Еще один служебный вход К служит для управлением матрицы. «0» на входе К разрешает отображение, «1» гасит матрицу.

И третий служебный вход С служит для защелкивания информации, поступающей на вход дешифратора. При высоком уровне на С сигнал немедленно дешифруется и подается на индикатор. При изменении его на «0» входной код защелкивается и отображается независимо от изменений на входе до тех пор, пока уровень на входе С снова не станет высоким. Запоминание происходит по спаду высокого уровня.

Выходные ключи микросхемы К176ИД2 в состоянии выдерживать токи короткого замыкания численно равные уровню питающего напряжения (в мА) и потому могут быть нагружены непосредственно на светодиодные индикаторы (к примеру, АЛ305, АЛС324, АЛС321) без дополнительных усилителей тока.

Микросхема К176ИДЗ

Полный аналог К176ИД2 по расположению выводов и алгоритму работы. Отличие заключается в выходных ключах, выполненных по схеме с открытым стоком. Это позволяет непосредственно подключать к выходу дешифратора аноды люминесцентных индикаторов, требующих для своего питания относительно высокого напряжения (до 15 В). При использовании микросхемы совместно с такими индикаторами на служебный вход S нужно подать лог. «0».

——————————————-

Микросхема 564ИД4

Дешифратор-преобразователь. Предназначен для преобразования двоичного кода в код для семисегментного (в том числе и ЖК) индикатора. Цепей для управления десятичной точкой нет.

Основное отличие от К176ИД2 – наличие третьего вывода для питания выходных ключей, которые выдерживают напряжение до 15 В. Для противофазного питания ЖКИ существует специальный усилитель (вход S, выход Р). Рассмотрим его работу подробнее на примере подключения ЖК индикатора ИЖКЦ1-1/18.

Основное отличие от К176ИД2 – наличие третьего вывода для питания выходных ключей, которые выдерживают напряжение до 15 В. Для противофазного питания ЖКИ существует специальный усилитель (вход S, выход Р). Рассмотрим его работу подробнее на примере подключения ЖК индикатора ИЖКЦ1-1/18.

Предположим, сам дешифратор как и все предыдущие узлы прибора питается напряжением 5 В (вывод16), а ЖК индикатору требуется переменное напряжение амплитудой 15 В. Для организации питания ЖКИ поступаем следующим образом: на вывод 7 подаем 15 В (третий вывод питания), а на вывод 6 (вход S) сигнал уровня ТТЛ (5 В) и частотой 100Гц. Этот сигнал проходит к выводу 1 (вывод Р) без инверсии, но амплитуда его увеличивается до напряжения 15 В.

Предположим, сам дешифратор как и все предыдущие узлы прибора питается напряжением 5 В (вывод16), а ЖК индикатору требуется переменное напряжение амплитудой 15 В. Для организации питания ЖКИ поступаем следующим образом: на вывод 7 подаем 15 В (третий вывод питания), а на вывод 6 (вход S) сигнал уровня ТТЛ (5 В) и частотой 100Гц. Этот сигнал проходит к выводу 1 (вывод Р) без инверсии, но амплитуда его увеличивается до напряжения 15 В.

Этот же сигнал при активном уровне (лог.1) инвертирует сигналы с выхода дешифратора (аналогично 176ИД2,3). Поскольку выходные ключи микросхемы питаются от источника 15 В, то уровень на них будет изменяться от 0 до 15 В с частотой 100 Гц, причем в противофазе с сигналом Р. Таким образом на активных сегментах индикатора будет присутствовать переменное напряжение, на неактивных – 0.

Стоит заметить, что дешифратор является полным – т.е. в состоянии отображать не только цифры от 0 до 9, но и символы «L», «Н», «Р», «А», «-» соответственно двоичному коду 10-14. При коде 15 все сегменты гасятся.

Хотя основное предназначение микросхемы – управление ЖК индикатором, ее выходной мощности достаточно для зажигания светодиодной матрицы (при напряжении питания до 10 В – даже без токоограничивающих резисторов). Изменяя уровень на входе S, можно питать матрицы как с общим анодом, так и с общим катодом. Выход Р при этом не используется.

——————————————-

Микросхема 564ИД5

Дешифратор отличается от 564ИД4 отсутствием выхода Р и имеет четырехразрядный регистр-защелку, аналогичную К176ИД2.

Управление регистром осуществляется по входу С: «1» — прямое прохождение кода на дешифратор и далее на выходы для подключения сегментов индикатора, «0» — защелкивание информации для отображения. В таком режиме микросхема не реагирует на изменение двоичного кода на входе. Защелкивание информации происходит в момент спада уровня на входе С.

Интересная особенность дешифраторов К176ИД2, К176ИД3, 564ИД4 и 564ИД5 – одинаковая разводка одноименных выводов входа и выхода.

——————————————-

Микросхема КР1561ИД6

Один корпус микросхемы содержит два независимых двоично-десятичных дешифратора на два входа и четыре выхода. Каждый дешифратор снабжен входом стробирования.

Активные уровни входа и выхода – высокие, входа стробирования – низкий. При «0» на входе S дешифратор работает (на выходе появляется десятичный эквивалент входного кода), при «1» — все выходы устанавливаются в «0».

Активные уровни входа и выхода – высокие, входа стробирования – низкий. При «0» на входе S дешифратор работает (на выходе появляется десятичный эквивалент входного кода), при «1» — все выходы устанавливаются в «0».

Микросхема КР1561ИД7

Полный аналог КР1561ИД6 по разводке и алгоритму функционирования, но на выходах обоих дешифраторов стоят инверторы (активный уровень выхода – низкий).

Из-за наличия инверсных выходов микросхема идеально подходит для управления большинством КМОП дешифраторов при их каскадном включении. На рисунке ниже в схеме управления группой К561ИД1 применен один дешифратор микросхемы КР1561ИД7, что позволило построить дешифратор с 32 выходами всего на пяти корпусах.

Из-за наличия инверсных выходов микросхема идеально подходит для управления большинством КМОП дешифраторов при их каскадном включении. На рисунке ниже в схеме управления группой К561ИД1 применен один дешифратор микросхемы КР1561ИД7, что позволило построить дешифратор с 32 выходами всего на пяти корпусах.

Для построения полного дешифратора на 8 выходов к микросхеме КР1561ИД6 (выходной код – прямой) или КР1561ИД7 (выходной код – инверсный) достаточно добавить всего один инвертор:

——————————————-

Дешифратор (декодер) – это комбинационное устройство с несколькими входами и выходами, у которого определенным комбинациям входных сигналов соответствует активное состояние одного из выходов. Дешифраторы преобразуют двоичный или двоично-десятичный код в унитарный код. Если декодер имеет n входов, m выходов и использует все возможные наборы входных переменных, то m = 2 n . Такой декодер называют полным. Если используется лишь часть наборов, то такой декодер называют неполным. Дешифраторы используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер устройства (его адрес) представлен двоичным кодом. Входы декодера (адресные входы) часто номеруют не порядковыми номерами, а в соответствии с весами двоичных разрядов, т. е. не 1, 2, 3, 4, а 1, 2, 4, 8.

Формально описать работу дешифратора можно, задав список функций, отрабатываемых каждым из его выходов Y i . Так, для дешифратора 3–8:

Y

o

=

;Y

1

=

;Y

2

=

;Y

2

=

;

Y

3

=

;

Y

3

= ;

... Y

7

=a

4 a

2 a

1 .

;

... Y

7

=a

4 a

2 a

1 .

Число входов и выходов декодера указывают следующим образом: декодер 3–8 (читается “три в восемь”); 4–16; 4–10 (это неполный дешифратор). Реализация указанных восьми выражений с помощью восьми трехвходовых элементов И (рис. 10.7) дает наиболее простой по структуре дешифратор, называемый линейным.

а б

Рис. 10.7. Дешифратор 3-8: а – условное обозначение; б – структура

Основной объем его оборудования в общем случае m n -входовых элементов И. Кроме того, к оборудованию обычно относят n инверторов входных переменных и n буферных входных усилителей, сводящих к единице кратность нагрузки источника сигнала.

Дешифраторы часто имеют разрешающий вход EI . При EI = 1 дешифратор работает как обычно, а при EI = 0 на всех выходах устанавливаются не активные уровни.

Вход EI воздействует на все элементы И. В схеме (рис. 10.8) воздействие оказывается через прямой и инверсный входы одного из разрядов входного кода (через дополнительные элементы И). При этом число входов элементов И не изменяется, но в работу дешифратора вносится дополнительная задержка. В схеме (рис. 10.9) задержка не вносится, но здесь элементы И имеют большее число входов.

Разрешающий вход EI часто выполняется инверсным. Дешифратор, имеющий разрешающий вход, иногда называют декодер–демультиплексор и вместо обозначения DC используют обозначение DX . Это связано с тем, что вход EI иногда используют в качестве информационного (как в демультиплексорах).

Рис. 10.8. Разрешение через прямой и Рис. 10.9. Разрешение через

инверсный входы одного из разрядов дополнительные входы элементов И

Вход EI используется при построении древовидных (каскадных) схем дешифраторов с целью расширения адресного пространства. При этом все адресное пространство разбивается на группы. Старшие разряды адреса подаются на дешифратор старших разрядов, выходы которого по входам EI управляют дешифраторами второго каскада. На рис. 10.10 представлена схема двухкаскадного дешифратора 5–32 (пять в тридцать два).

Рис. 10.10. Двухкаскадный дешифратор 5–32

Два старших разряда адреса а 16 и а 8 расшифровываются дешифратором 2–4 DC 4, который по входам Е I управляет четырьмя дешифраторами второго каскада. Младшие разряды адреса а 4 , а 2 , а 1 поступают на все дешифраторы второго каскада, но открытым по входу EI оказывается лишь один из них. Ему и будет принадлежать единственный из всех 32 возбужденный выход. Например, входной код 01111 у дешифратора DC 4 делает активным выход 1. Этим сигналом и откроется дешифратор второй ступени DC 1, а DC 0, DC 2, DC 3 закрыты. У дешифратора DC 1 сигнал появится на выводе 7, что соответствует 15 выходу всего дешифратора. Такой принцип используется при построении дешифратора на много выходов из микросхем дешифраторов с меньшим числом выходов.

В рассмотренном случае 5-разрядный адрес был разбит на две группы в 2 и 3 разряда. Это и определило структуру дешифратора. В общем случае многоразрядный адрес можно разбить на группы различными способами и каждому будет соответствовать свой вариант схемы. Варианты будут различаться задержкой и аппаратными затратами. Таким образом, можно ставить задачу выбора оптимальной, в заданной серии элементов, структуры.

На рис. 10.11 показан двухкаскадный дешифратор 4–16, второй каскад которого собран по схеме прямоугольного дешифратора. Разряды адреса разбиты на две группы, каждая из которых независимо от другой расшифровывается своим дешифратором первого каскада DC 0 и DC 1. При любой комбинации значений входных переменных оказываются выбранными одна строка и один столбец сетки, в узлах которой расположены элементы И второй ступени (второго каскада). В результате каждый входной набор возбуждает выход единственного соответствующего ему элемента И. Такую сетку из элементов И называют прямоугольным или матричным дешифратором.

Рис. 10.11. Матричный дешифратор

Делить разряды адреса между DC 1 и DC 2 нужно по возможности поровну. Чем ближе прямоугольник второго каскада к квадрату, тем, при том же числе выходных элементов И, меньше сумма его строк и столбцов, т. е. меньше число выходов дешифраторов первого каскада. Из этого следует, что использование во втором каскаде квадратной матрицы, позволяет применить в первом каскаде наиболее простые дешифраторы и тем самым минимизировать общую задержку в работе всего дешифратора.

В качестве входа EI (Е ) всего двухкаскадного дешифратора удобно использовать разрешающий вход только одного из дешифраторов первого каскада. При этом запираются или все строки или все столбцы.

Следует отметить, что при большом числе выходов (сотни и более) прямоугольный дешифратор самый экономичный по оборудованию, чем и объясняется его применение в БИС памяти. При малом числе выходов наиболее экономичным является линейный дешифратор.

Дешифраторы, выпускаемые в виде микросхем, имеют буквенное обозначение ИД, например, 155ИД3, 155ИД4. В сериях ТТЛ дешифраторы имеют обычно инверсные выходы, т. е. активным является низкий уровень. В КМОП-сериях выходные сигналы чаще имеют активный высокий уровень.

Часто в микросхемах дешифраторов делают несколько разрешающих входов, а разрешающей комбинацией является их конъюнкция. При этом удобно наращивать дешифраторы, используя каскадный принцип и строя первый каскад дешифрации не на отдельном специальном дешифраторе, а собирая его из конъюнкторов разрешающих входов. На рис. 10.12 представлен дешифратор 5–32 из 4 дешифраторов 3–8. Каждая микросхема имеет два инверсных разрешающих входа. Символ & над символом Е I обозначает, что разрешение существует лишь при совпадении всех сигналов группы входов, помеченных знаком &. На рисунке символы инверсии указывают на совпадение двух низких уровней на входах разрешения.

Дешифратор первого каскада распределен по конъюнкторам 4 микросхем. Такое решение – иметь несколько разрешающих входов, связанных операцией И, чтобы собирать на этих входах фрагменты дешифраторов, вообще типично для современных микросхем .

Рис. 10.12. Дешифрация адресов с использованием в первом каскаде разрешающих входов

Если использовать только два дешифратора DC 0 и DC 1, то можно получить дешифратор на 16 выходов. При этом адресный вход а 16 будет отсутствовать, а нижние (по схеме) разрешающие входы дешифраторов DC 0 и DC 1 должны быть заземлены.

Схема дешифратора 155ИД4 представлена на рис. 10.13. В нее входят два дешифратора 2–4. Каждый дешифратор имеет пару разрешающих входов. Один разрешающий вход одной из секций инвертирован. Это позволяет, объединив его с неинвертированным разрешающим входом другой секции и подав на эту пару третью переменную а 4 , использовать ту же самую схему как дешифратор 3–8 с разрешающим входом Е . Кроме того, эта микросхема может быть использована как два демультиплексора с 1 входа на 4 выхода и как демультиплексор с одной линии на 8 выходов.

Рис. 10.13. Схема дешифратора 155ИД4.

Рис. 10.14. Варианты подключения дешифратора 155ИД1

На рис. 10.14 показана возможность использования микросхемы 155ИД1 в качеств дешифратора 4–10 или 3–8. В представленной схеме при использовании всех четырех входов в качестве адресных микросхема представляет дешифратор 4–10. Если вход 8 использовать в качестве разрешающего входа, тогда микросхема будет служить дешифратором 3–8. Выходы 8 и 9 при этом не используются.

Дешифраторы могут применяться в качестве демультиплексора входных сигналов, а совместно с шифратором находят применение при построении преобразователей кодов, селектировании заданных входных кодов и др. . Для реализации подобных устройств могут быть использованы программируемые логические матрицы или программируемые логические интегральные схемы (ПЛМ или ПЛИС) .

Дешифратор К155 ИД3, К1533ИД1

Микросхема представляет собой двоично-десятичный дешифратор на 15 выходов.

Выводы 23, 22, 21 20 — информационные. Служат для получения двоичного кода с весом разрядов 1, 2, 4, 8 соответственно. При получении кода, микросхема выставляет логический «0» на соответствующем коду десятичном выходе (выводы 1-17). На всех остальных выходах в это время присутствует «1».

Все вышесказанное справедливо лишь в том случае, если на входах S (выводы 18, 19), соединенных по «И», присутствует «0». Если на любом из выводов появится «1», на всех выходах дешифратора установится «1» независимо от входного кода. Таким образом, используя входы S и всего лишь один инвертор, несложно нарастить разрядность дешифратора до 32:

Еще один инвертор позволит увеличить разрядность до 64:

Если требуется получить дешифратор на большее количество разрядов, то в качестве устройства выбора микросхем вместо инверторов лучше использовать ту же ИД3 (на схеме ниже – DD1).

В зависимости от четырех старших разрядов кода она активирует тот или иной дешифратор, организуя полную байтную линейку (8 двоичных входов, 256 десятичных выходов).

——————————————-

Дешифтратор К155ИД4, К555ИД4, КР1533ИД4

Микросхема представляет собой два идентичных двоично-десятичных дешифратора на два входа (двоичный код с весом 1-2) и четыре выхода (десятичный код 0-3) каждый. Адресные двоичные входы дешифраторов включены параллельно (выводы 3, 13 микросхемы).

Каждый дешифратор имеет свои входы стробирования. У верхнего по схеме дешифратора входы стробирования соединены по «И», назначение их аналогично микросхеме ИД3 – логический «0»на обоих входах разрешает дешифрацию, «1» на любом из них переводит все выходы дешифратора в «1». Нижний по схеме дешифратор имеет стробирующие входы, соединенные по «И», но с инверсией одного из них. Таким образом дешифрация произойдет при наличии на стробирующих входах сигналов «1» и «0» При любой другой комбинации работа дешифратора будет запрещена (на всех выходах «1»). Такая организация позволяет построить дешифратор на 8 всего на одном корпусе без применения дополнительных элементов:

Аналогично микросхеме ИД3 в дешифраторах на микросхемах ИД4 несложно нарастить разрядность:

При необходимости количество выходов ИД4 можно дорастить до 10 и превратить его в неполный двоично-десятичный дешифратор на 4 входа и 10 выходов используя простую логику:

Разводку выводов питания ТТЛ микросхем серии К155 (1533, 555, 133) можно посмотерть .

Разводку выводов питания ТТЛ микросхем серии К155 (1533, 555, 133) можно посмотерть .

——————————————-

Микросхема К555ИД5

Является аналогом 155ИД4 с той лишь разницей, что выходы дешифратора собраны по схеме с открытым коллектором:

Разводку выводов питания ТТЛ микросхем серии К155 (1533, 555, 133) можно посмотерть .

——————————————-

Микросхема К155ИД1

Неполный двоично-десятичный дешифратор на 4 входа и 10 выходов. Отличительная особенность микросхемы – высоковольтные выходные ключи с открытым коллектором. Микросхема имеет минимум управления — 4 входа для подачи двоичного кода и 10 выходов для отображения полученного кода в десятичном счислении (плюс два вывода питания).

Вход управляется уровнями ТТЛ. Выходы можно нагрузить (собственно для этого микросхема и предназначена) высоковольтными газоразрядными индикаторами, питающимися постоянным или пульсирующим напряжением до 300 В. При поступлении на входы 3, 6, 7, 4 двоичного кода, соответствующий этому коду выход соединяется с корпусом (- источник питания). Все остальные выходы в это время закрыты (имеют высокое сопротивление – «обрыв»). Если на вход подать двоичный эквивалент чисел 10-15 (четырехразрядный двоичный вход это позволяет), то все выходы микросхемы окажутся отключенными. Схема подключения газоразрядного индикатора к микросхеме 155ИД1 проста:

Катоды разрядов подключаются к выходам дешифратора, общий анод через резистор R1 (минимум 22кОм) к плюсу источника питания газоразрядного индикатора. Минус этого источника соединяется с минусовым проводом питания микросхемы.

Разводку выводов питания ТТЛ микросхем серии К155 (1533, 555, 133) можно посмотерть .

——————————————-

Микросхема К555ИД6

Неполный двоично-десятичный дешифратор, работающий по тому же алгоритму, что и 155ИД1. Единственное отличие — выходы ИД6 имеют обычные ключи, выдающие ТТЛ уровни «0», «1».

При получении двоичного кода, микросхема устанавливает на соответствующем выходе уровень «0», на остальных «1». При входном коде 10-15 на всех выходах присутствует «1».

Разводку выводов питания ТТЛ микросхем серии К155 (1533, 555, 133) можно посмотерть .

——————————————-

Микросхема К555ИД7, КР1533ИД7, КР531ИД7

Полный двоично-десятичный дешифратор на 3 входа и восемь выходов. Входы служат для подачи трехразрядного двоичного кода, выходы – для выдачи его десятичного эквивалента (активный уровень низкий).

Для стробирования выходного сигнала служат три входа S соединенные по «И», два из которых инверсные. При наличии на входах 4, 5, 6 уровней «0», «0», «1» соответственно, дешифрация разрешена, при любой другой комбинации на всех выходах дешифратора устанавливается высокий уровень. Благодаря расширенному управлению стробирования дешифраторы можно объединять для наращивания разрядности без дополнительных элементов или с их минимумом. В качестве примера ниже приведена схема дешифратора на 32 разряда с использованием всего одного дополнительного инвертора.

Разводку выводов питания ТТЛ микросхем серии К155 (1533, 555, 133) можно посмотерть .

——————————————-

Микросхема К155ИД10, К555ИД10

Неполный двоично-десятичный дешифратор на четыре входа и десять выходов.

По расположению выводов и логике работы аналогичен микросхеме К155ИД6, но выходы ИД10 выполнены по схеме с открытым коллектором, а выходные ключи рассчитаны на достаточно большой выходной ток. При низком уровне на выходе ключ 555 серии дешифратора в состоянии держать ток до 24 мА, 155 и 133 серии – до 80 мА. При отключенном выходе всех серий напряжение на нем может достигать 15 В, что позволяет напрямую запитать маломощное электромагнитное реле:

Разводку выводов питания ТТЛ микросхем серии К155 (1533, 555, 133) можно посмотерть .

——————————————-

Микросхема КР531ИД14, КР1533ИД14

Два полных двоично-десятичных дешифратора с двухразрядным входом и четырехразрядным десятичным выходом каждый.

При подаче на вход двоичного двухразрядного кода на соответствующем выходе дешифратора устанавливается его десятичный эквивалент. Входы у обоих дешифраторов прямые, выходы инверсные. Кроме того, каждый из дешифраторов стробируется отдельным сигналом S (вход инверсный). При наличии «0» на входе стробирования дешифратор работает, при высоком уровне переводит все выходы в состояние «1».

Как и все дешифраторы КР1533(531)ИД14 могут соединяться каскадно для наращивания разрядности. На рисунке ниже представлена схема неполного дешифратора на 4 входа и 12 выходов, составленная из двух корпусов КР531ИД14.

Разводку выводов питания ТТЛ микросхем серии К155 (1533, 555, 133) можно посмотерть .

——————————————-

Дешифраторы позволяют преобразовывать одни виды бинарных кодов в другие. Например, преобразовывать позиционный двоичный код в линейный восьмеричный или шестнадцатеричный. Преобразование производится по правилам, описанным в таблицах истинности, поэтому построение дешифраторов не представляет трудностей. Для построения дешифратора можно воспользоваться правилами .

Десятичный дешифратор

Рассмотрим пример разработки схемы дешифратора из двоичного кода в десятичный. Десятичный код обычно отображается одним битом на одну десятичную цифру. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Сигнал с этих выводов можно подать на . В простейшем случае над светодиодом можно просто подписать индицируемую цифру.Таблица истинности десятичного дешифратора приведена в таблице 1.

Таблица 1. Таблица истинности десятичного дешифратора.

| Входы | Выходы | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 8 | 4 | 2 | 1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Микросхемы дешифратора на принципиальных схемах приведено на рисунке 2. На этом рисунке приведено обозначение двоично-десятичного дешифратора, полная внутренняя принципиальная схема которого изображена на рисунке 1.

Рисунок 2. Условно-графическое обозначение двоично-десятичного дешифратора

Точно таким же образом можно получить принципиальную схему и для любого другого декодера (дешифратора). Наиболее распространены схемы восьмеричных и шестнадцатеричных дешифраторов. Для индикации такие дешифраторы в настоящее время практически не используются. В основном такие дешифраторы используются как составная часть более сложных цифровых модулей.

Семисегментный дешифратор

Для отображения десятичных и шестнадцатеричных цифр часто используется . Изображение семисегментного индикатора и название его сегментов приведено на рисунке 3.

Рисунок 3. Изображение семисегментного индикатора и название его сегментов

Для изображения на таком индикаторе цифры 0 достаточно зажечь сегменты a, b, c, d, e, f. Для изображения цифры "1" зажигают сегменты b и c. Точно таким же образом можно получить изображения всех остальных десятичных или шестнадцатеричных цифр. Все комбинации таких изображений получили название семисегментного кода.

Составим таблицу истинности дешифратора, который позволит преобразовывать двоичный код в семисегментный. Пусть сегменты зажигаются нулевым потенциалом. Тогда таблица истинности семисегментного дешифратора примет вид, приведенный в таблице 2. Конкретное значение сигналов на выходе дешифратора зависит от к выходу микросхемы. Эти схемы мы рассмотрим позднее, в главе, посвящённой отображению различных видов информации.

Таблица 2. Таблица истинности семисегментного дешифратора

| Входы | Выходы | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 8 | 4 | 2 | 1 | a | b | c | d | e | f | g |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

В соответствии с принципами построения произвольной таблицы истинности по произвольной таблице истинности получим принципиальную схему семисегментного дешифратора, реализующего таблицу истинности, приведённую в таблице 2. На этот раз не будем подробно расписывать процесс разработки схемы. Полученная принципиальная схема семисегментного дешифратора приведена на рисунке 4.